해당 포스팅은 학교 수업 내용을 요약정리하는것에 초점을 두고 진행합니다. (3학년 2학기과정 OS수업)

참고문헌 : OSTEP(Operating System : Three Easy Pices)

1. Summary and Intro

페이징에 대한 내용을 먼저 본 뒤, 해당 포스팅을 보시면 더욱 도움이 됩니다!

[OS] 페이징(paging)이란?

해당 포스팅은 학교 수업 내용을 요약정리하는것에 초점을 두고 진행합니다. (3학년 2학기과정 OS수업) 참고문헌 : OSTEP(Operating System : Three Easy Pices) 1. Summary and Intro 과연 세그먼트 방식은 완벽할

baejun.tistory.com

2. What is page table?

직전 포스팅에서 다뤘듯이, 외부 단편화문제를 해결하고자 페이징 기법을 사용했다.

페이징 기법은 "고정크기로 조각을 낸 불연속적인" 공간을 할당했는데, 그 불연속성을 가능케 하는게 page table이라 언급했었다. 그래서 page table이 뭔데?

를 알아보기 전에, 한 가지 짚고 넘어가자.

모든 논리 주소는 결국 실존하지 않는 정보이고, 따라서 모든 논리 주소에 대한 정보는 물리 메모리 어딘가에 저장되어 있어야 한다.

그렇다면, 해당 논리주소에 대한 정보가 물리 메모리 어디에 있는데? 에 대한 답이 필요하다.

그 답은 바로 페이지 테이블에 담겨있다 !

그림에서 보이듯, 논리 주소공간에서 물리 주소공간으로 "주소 변환"이 일어날때

페이지 테이블을 통해 위치 정보를 획득하고 매핑하게 된다.

즉 논리공간에 "A"라는 정보는 물리공간 "B"에 저장 되어 있다고 가정하면

페이지 테이블에서 "A는 B로 가면 됨"과 같은 정보를 담고 전달하는 것이다.

따라서 물리 주소공간에서 Process A와 B가 뒤죽박죽 막 섞여있더라도, 첫번째 실행조각은 어디로 가야된다 ~~

두번째 실행조각은 어디로 가야된다 ~~ 하는 정보를 page table을 통해 알고 가기때문에

쪼개져 있는 조각조각의 page를 LINEAR(선형적,일렬로)하게 실행할 수 있게된다!

* 각 프로세스마다 논리 주소를 가지므로, 당연히 프로세스마다 별도의 페이지 테이블 자료구조를 가지게 된다!!

그리고 당연히 페이지 테이블의 정보 또한 물리 메모리에 저장되어 있어야 한다.

페이지 테이블의 정보는 물리메모리에 커널 메모리 영역에 저장되게 된다.

3. 논리 주소의 구성

자 그럼 이제 이 주소 변환 과정에 대해서 조금 더 알아보자.

먼저 논리 주소의 구성부터 알아야 한다.

논리 주소는 가상 페이지 번호(VPN)와 오프셋(offset)으로 구성되어 있다.

64 바이트의 논리 주소 공간에 필요한 비트 수는 6bit이다. (2^6 = 64)

그리고 그 6bit를 VPN과 offset으로 분리하는데, VPN은 가상 페이지의 번호정보를 나타내고, Offset은 그 페이지 내 에서의 위치를 나타낸다.

쉽게 말해서, 고정 크기로 조각 조각낸 페이지의 단위를 VPN, 그 한 조각 안에서의 위치를 offset이라고 생각하면 되겠다.

그래도 이해가 안간다면, 통짜 건물을 총 10층 짜리로 나누는 단위가 VPN, 그리고 각 층마다 1호 2호 호수를 offset이라고 생각해보자.

계속해서 위 예제 내용으로 주소공간에 21을 주소공간에 이동시킬 때, 21을 이진수로 나타내면 10101이다.

01 / 0101로 1번페이지의 5번공간~ 이라고 생각하면 되겠다.

그리고 주소 변환을 실행하게되는데, 이 때 중요한건 offset은 동일하다는거다.

왜냐? 논리 주소와 물리주소를 똑같은 크기로 잘라놨기 때문에 그 내부에서의 위치는 동일하다는 것이다.

따라서 offset은 그대로 copy하고, VPN(가상 페이지 번호)를 주소 변환을 통해 물리주소의 PFN(페이지 프레임 넘버)로 매핑 시켜주면 되겠다.

* 주소 변환은 MMU hardware로 진행한다.

전체적인 주소변환의 흐름이다.

위에 설명을 잘 따라왔다면 눈에 금방 들어올 것이다.(p = VPN, f = PFN, d = offset)

4. 페이지 테이블 항목(page table entry, PTE)

테이블 번호(VPN)안에 내용물이라고 생각하면 되겠다.

여기엔 당연히 각 물리 주소 변환 정보가 저장되어있다.

PTE의 개수는 논리 주소와 물리 주소간에 매핑 정보를 다 담고 있기 때문에, 논리 주소만큼의 개수를 가지게 된다.

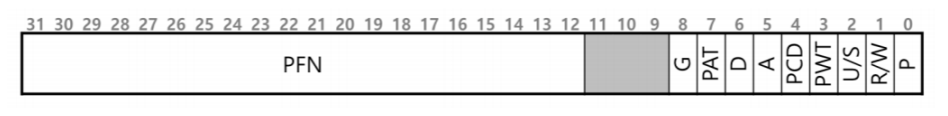

PTE에는 다음과 같은 항목들이 저장되어 있다.

- Valid bit: 현재 물리 메모리를 사용하는지 판단하기 위한 비트(이미 물리메모리에 접근했는지)

- Protection bit : 읽기/쓰기/실행 권한을 설정하는 비트

- Present bit : 현재 물리 메모리에 상주하는지 판단하기 위한 비트(for 스왑 파티션)

- Dirty bit : 메모리의 내용이 수정되었는지 판단하기 위한 비트( A -> A' 업데이트 되었으면 dirty해졌다 표현)

- Reference bit : 페이지가 접근 되었는지 판단하기 위한 비트(아무도 참조 안했으면 재사용 가능)

5. 페이지 테이블의 크기 구하기 예제

예제:

1. 가상 주소 : 32bits

2. 물리 주소 : 20bits

3. 페이지 크기 : 4KB

일때

offset = 4KB = 12bits

VPN = 32bits - offset bits(12bits) = 20bits

페이지 테이블 엔트리 = 2^20

페이지 테이블의 크기 = 4byte * 2^20 = 4MB

다음 장에선 페이징의 문제점에 대해 다뤄보겠다 !!!

'OS' 카테고리의 다른 글

| [OS] TLB - Paging의 성능문제에 대한 해결책 (0) | 2022.12.17 |

|---|---|

| [OS] 페이징(paging)이란? (0) | 2022.11.20 |